SyncSim is a simulator framework capable of loading different simulator modules. It is used today with a module that simulates hardware models described with Java. This simulator module is used together with a model of a MIPS processor core in courses given at EISLAB.

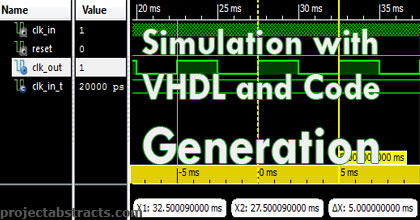

The purpose of this thesis is to create a new simulator module for SyncSim which can use hardware models described with a mixture of VHDL and Java and to implement a C compiler that can generate code compatible with the existing MIPS model.

EESim is a simulator module for an early version of SyncSim that uses VHDL to describe the hardware model. This simulator module will be extended to meet the requirements of the new simulator. The Portable C Compiler (PCC) has previously been released as open source and work has been done by others to modernize it. PCC will be ported to the MIPS architecture and its portability evaluated.

Simulation with VHDL and Code Generation

The result is a new version of EESim that can simulate models which mix VHDL and Java, and a PCC port capable of producing MIPS assembly code. With regards to portability PCC was found to be relatively easy to modify for use on a new computer architecture.

Authors: Jan Enoksson, Simon Olsson

Source: Luleå University of Technology

>> Electronics Mini Projects for ECE